HSA

BENJAMIN COQUELLE

MAY 2015

## HAS MEMBERS

## **HSA MEMBERS**

#### **Contributors**

#### **Academics**

#### **HSA GOALS**

- Defines a set of low level software components (HSAIL, memory management...)

- Manages work queues to the HSA devices (fast enqueue and signaling)

- Gives simple access to CPU and GPU in the APU

- Single address space for CPU and GPU

- High level languages and compiler target HSA runtime and hardware to expose all the features to all the developers

- OpenCL 2.0, C++, Fortran, OpenMP 4,....

- http://www.hsafoundation.com/

- https://github.com/hsafoundation

- OpenMP and C/C++ : <a href="https://github.com/HSAFoundation/HSA-OpenMP-GCC-AMD">https://github.com/HSAFoundation/HSA-OpenMP-GCC-AMD</a>

- HSA runtime: <a href="https://github.com/HSAFoundation/HLC-HSAIL-Development-LLVM">https://github.com/HSAFoundation/HLC-HSAIL-Development-LLVM</a>

- HSAIL-LLVM: <a href="https://github.com/HSAFoundation/HSA-Runtime-Reference-Source">https://github.com/HSAFoundation/HSA-Runtime-Reference-Source</a>

## HSA FEATURES ON AMD APUS

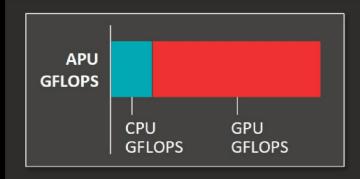

#### **UNLOCKING All APU GFLOPS**

Access to full potential of APU compute power

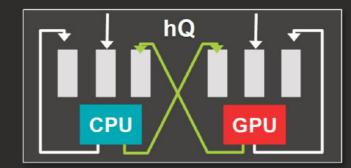

#### **ALL CORES EQUAL**

- Heterogeneous queuing (hQ) defines how processors interact equally

- ▲ GPU and CPU have equal flexibility to create/dispatch work

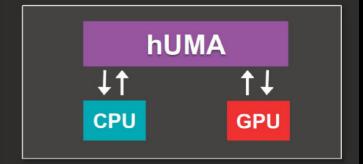

#### **EQUAL ACCESS TO ENTIRE MEMORY**

✓ First time ever: GPU and CPU have uniform visibility into entire memory space

UNLOCKS THE UNMATCHED COMPUTE POTENTIAL AND EFFICIENCY OF APUS

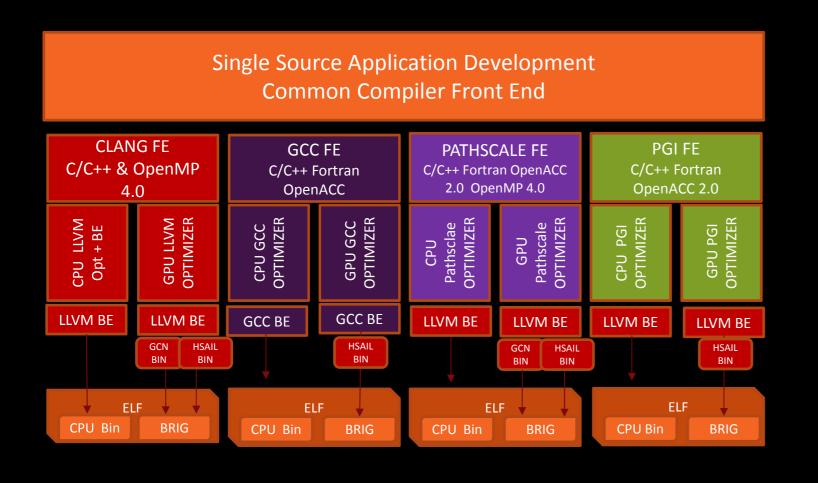

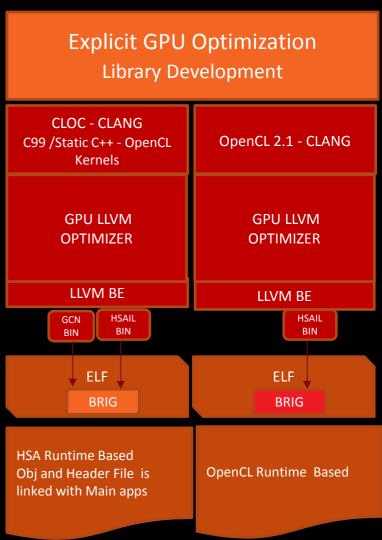

### SIMPLIFIED DEVELOPMENT - GIVING YOU CONTROL WHEN YOU NEED IT

PARTNERS WILL LEVERAGE OUR CODE GENERATORS

### KALMAR-C++

- An Open Source implementation contributed by MulticoreWare

- Based on Clang & LLVM 3.3 and 3.5

- Lower C++ AMP codes to:

- OpenCL SPIR

- OpenCL C

- HSA HSAIL / BRIG

- x86-64 (CPU fallback)

- Compatible with all major OpenCL stacks, and HSA

- https://bitbucket.org/multicoreware/cppamp-driver-ng/wiki/Home

# **OPENCL 2.0 MEMORY MANAGEMENT**

####

```

FINE GRAIN BUFFER SVM

```

```

//CL MEM SVM FINE GRAIN BUFFER means host and device can

//concurrently access the buffer, thus no more data

//transfer....

float* Buffer = (float*)clSVMAlloc(ctx, CL MEM READ WRITE |

CL MEM SVM FINE GRAIN BUFFER,

1024 * sizeof(float), 0);

//fill the buffer from host, no data transfer

for (int i=0; i<1024; i++)

Buffer[i] = \dots;

// use your SVM buffer in you OpenCL kernel on device

directly

clSetKernelArgSVMPointer(my kernel, 0, Buffer);

clEnqueueNDRangeKernel(queue, my kernel,...)

```

```

//create device buffer

cl mem DeviceBuffer = clCreateBuffer(ctx,

CL MEM READ WRITE, 1024*sizeof(float), NULL, &err

);

//create host buffer

float* hostBuffer = new float[1024];

for (int i=0; i<1024; i++)

hostBuffer ] = ....;

//data transfer happens here

clEnqueueWriteBuffer(queue, DeviceBuffer,..., hostBuffer);

//use our device buffer on device

clSetKernelArg(my kernel, 0, sizeof(cl mem), &DeviceBuffer );

clEnqueueNDRangeKernel (queue, my kernel,...)

```

### **OPENCL 2.0 MEMORY MANAGEMENT**

#### FINE GRAIN SYSTEM

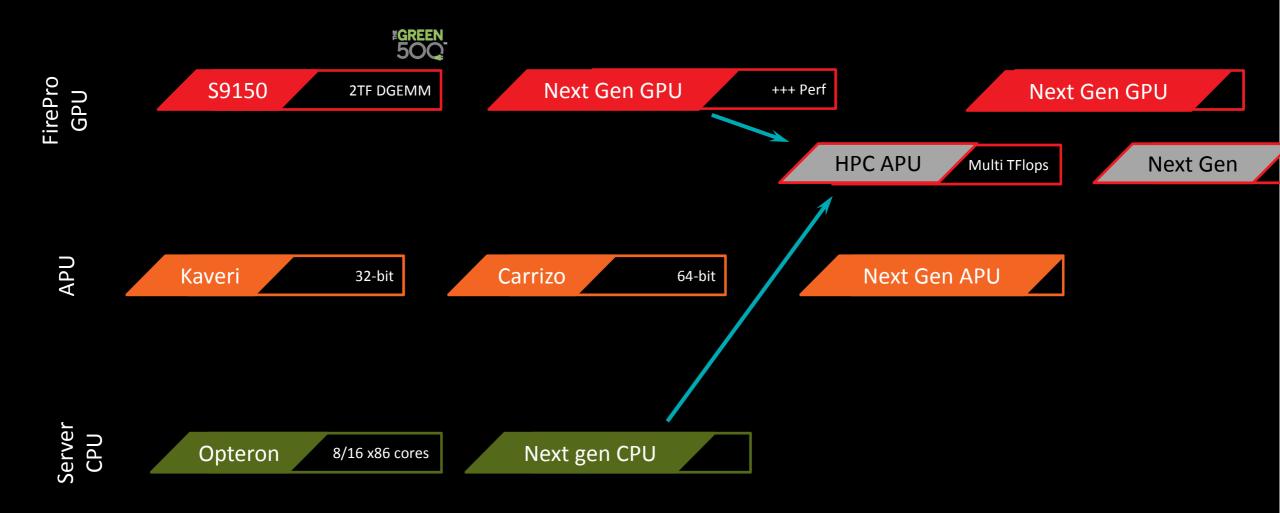

## **AMD HPC Roadmap Trends**

## AMD HSA HARDWARE

Kaveri APU – 2014

- Carrizo APU 2015

- http://www.amd.com/en-us/press-releases/Pages/amd-discloses-architecture-2015feb23.aspx

- **△** "**HPC APU"** beyond 2016

- Multi-Teraflops APU for servers and workstation

## **Develop your code now for tomorrow's platforms**

✓ Now

Best performance with FirePro GPU

▲ Summer 2015 AMD Carrizo APU x86 64-bit laptop for code testing

#### **Code portability**

## **Introducing AMD Compute Toolkit (ACT)**

Performance, Power, Productivity

Comprehensive developer solution providing ultimate performance and power efficiency while enhancing productivity

#### ▲ ACT includes

- AMD Compute SDK supporting the latest OpenCL APIs from Khronos

- AMD CodeXL a tool suite with leading-edge performance and power profilers, code analyzers and debuggers

- AMD's accelerated compute libraries

- Documentation and training to get you up to speed fast

- Developer support forums to get your questions answered quickly

- Find everything you need in one place with ACT

Delivering full potential from the heterogeneous resources on your platform http://developer.amd.com/

### **AMD CodeXL 1.7**

- Debug, Profile and Analyze applications

- On local and remote hosts

- ✓ Power Profiling

- ▲ AMD CPUs, GPUs and APUs

- Multiple platforms and Operating Systems

- Standalone application for Windows® and Linux®

- Integrated into Microsoft® Visual Studio®

- ✓ Free to download and use

http://developer.amd.com/tools-and-sdks/opencl-zone/codexl/

### DISCLAIMER & ATTRIBUTION

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions and typographical errors.

The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION.

AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **ATTRIBUTION**

© 2015 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions. Other names are for informational purposes only and may be trademarks of their respective owners.